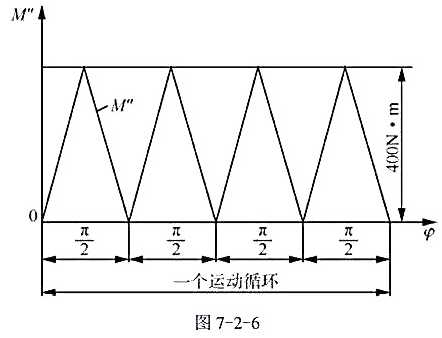

题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

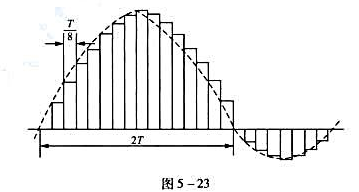

试设计一个系统使它可以产生图5-23所示的阶梯近似Sa函数波形(利用数字电路等课程知识).近似函

数宽度截取8T(中心向左右对称),矩形窄脉冲宽度T/8.每当一个“1"码到来时(由速率为2π/T的窄脉冲控制)即出现Sa码波形(峰值延后4T).

(1)画出此系统逻辑框图和主要波形;

(2)考虑此系统是否容易实现;

(3)在得到上述信号之后,若要去除波形中的小阶梯,产生更接近连续Sa函数的波形需采取什么办法?

答案

答案

请输入或粘贴题目内容

搜题

请输入或粘贴题目内容

搜题

拍照、语音搜题,请扫码下载APP

拍照、语音搜题,请扫码下载APP

题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

数宽度截取8T(中心向左右对称),矩形窄脉冲宽度T/8.每当一个“1"码到来时(由速率为2π/T的窄脉冲控制)即出现Sa码波形(峰值延后4T).

(1)画出此系统逻辑框图和主要波形;

(2)考虑此系统是否容易实现;

(3)在得到上述信号之后,若要去除波形中的小阶梯,产生更接近连续Sa函数的波形需采取什么办法?

答案

答案

更多“试设计一个系统使它可以产生图5-23所示的阶梯近似Sa函数波形(利用数字电路等课程知识).近似函”相关的问题

更多“试设计一个系统使它可以产生图5-23所示的阶梯近似Sa函数波形(利用数字电路等课程知识).近似函”相关的问题

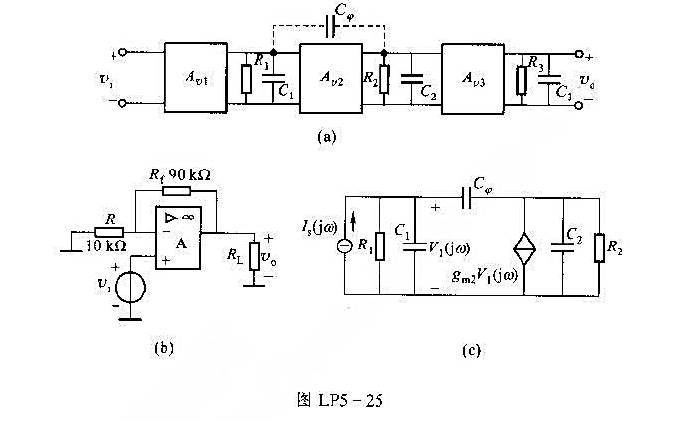

第1题

定,已知 若把它接成图LP5-25(b)所示的同相放大电路,为保证反馈放大器稳定工作,可采用简单电容补偿,亦可采用如图LP5-25(c)所示的密勒电容补偿,图中gm= 试求两种补偿时所需的电容值.设密勒补偿时

试求两种补偿时所需的电容值.设密勒补偿时 各级的输入和输出电阻对电路影响忽略不计.

各级的输入和输出电阻对电路影响忽略不计.

第5题

第6题

第7题

(1)画出系统的ASM图。

(2)画出系统的状态转换图。

(3)用Verilog HDL语言描述其工作过程。

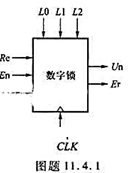

提示:数字锁系统的示意图如图题11.4.1所示,由于开锁过程比较简单,所以没有划分控制单元和处理单元。L0、L1、L2用于从到高位设置密码,另外三个输入端Re,En,Ki中,Re是复位端,当Re=

1时,系统复位进入初始状态;En是控制井关,Ki是数据输入端,当按一下En键使En=1时,从Ki端输入一个数码,再按一下En键,再送一个数码,直到将三个数码送完为止。每输入一个数据都要同原设定的密码比较,依次从低位到高位进行。若相等则准备接收下一位数码,若不相等,系统应进入错误状态。输入数码的位数也是开锁的条件。当输入数码的位数和位值与相应密码都相等时,系统发出开锁信号Un=1,锁被打开,否则Er=1表示开锁过程错误。为保密起见,中间错误状态不显示,并且不能返回初态,直到三个数码全部送完为止。

第8题

第10题

第11题