题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

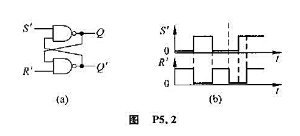

画出图P5.2(a)中SR锁存器输出端Q和Q'的电压波形。输入端S'和R'的电压波形如图P5.2(b)

画出图P5.2(a)中SR锁存器输出端Q和Q'的电压波形。输入端S'和R'的电压波形如图P5.2(b)所示。

答案

答案

请输入或粘贴题目内容

搜题

请输入或粘贴题目内容

搜题

拍照、语音搜题,请扫码下载APP

拍照、语音搜题,请扫码下载APP

题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

画出图P5.2(a)中SR锁存器输出端Q和Q'的电压波形。输入端S'和R'的电压波形如图P5.2(b)所示。

答案

答案

更多“画出图P5.2(a)中SR锁存器输出端Q和Q'的电压波形。输入端S'和R'的电压波形如图P5.2(b)”相关的问题

更多“画出图P5.2(a)中SR锁存器输出端Q和Q'的电压波形。输入端S'和R'的电压波形如图P5.2(b)”相关的问题

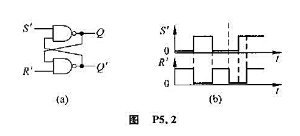

第1题

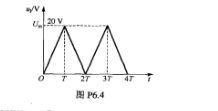

由主从JK触发器和555定时器组成的电路如图6.17(a)所示.已知CP为10Hz的方波,如图6.17(b)所示.R1=10kΩ、R2=56kΩ、C1=1000pF、C2=4.7uF,触发器Q端及555输出端(3端)初态均为“0".

(1)试画出Q端,u1、uO相对于CP脉冲的波形.

(2)试求Q端输出波形的周期.

第2题

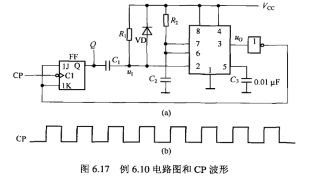

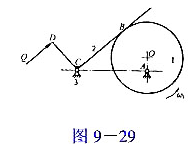

JK触发器组成图3.3(a)所示电路.试分析电路的逻辑功能.已知电路CLK和A的输入波形如图3.3(b)所示.设Q输出初态为0,画出Q的波形.

第3题

(1)画出系统的ASM图。

(2)画出系统的状态转换图。

(3)用Verilog HDL语言描述其工作过程。

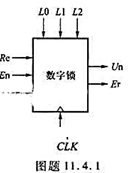

提示:数字锁系统的示意图如图题11.4.1所示,由于开锁过程比较简单,所以没有划分控制单元和处理单元。L0、L1、L2用于从到高位设置密码,另外三个输入端Re,En,Ki中,Re是复位端,当Re=

1时,系统复位进入初始状态;En是控制井关,Ki是数据输入端,当按一下En键使En=1时,从Ki端输入一个数码,再按一下En键,再送一个数码,直到将三个数码送完为止。每输入一个数据都要同原设定的密码比较,依次从低位到高位进行。若相等则准备接收下一位数码,若不相等,系统应进入错误状态。输入数码的位数也是开锁的条件。当输入数码的位数和位值与相应密码都相等时,系统发出开锁信号Un=1,锁被打开,否则Er=1表示开锁过程错误。为保密起见,中间错误状态不显示,并且不能返回初态,直到三个数码全部送完为止。

第6题

第7题

第9题

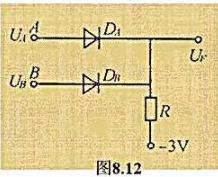

图8.12(教材8.01)所示电路中的UA=0V,UB=1V,试求下述情况下输出端的电压UF。

(1)二极管为理想二极管;

(2)二极管为锗二极管;

(3)二极管为硅二极管。