题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

M法的原理是由计数器记录PLG发出的脉冲信号;定时器每隔时间Tc向CPU发出中断请求INTt;CPU响应中断后,读出计数值M1,并将计数器清零重新计数。()

答案

答案

请输入或粘贴题目内容

搜题

请输入或粘贴题目内容

搜题

拍照、语音搜题,请扫码下载APP

拍照、语音搜题,请扫码下载APP

题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

答案

答案

更多“M法的原理是由计数器记录PLG发出的脉冲信号;定时器每隔时间Tc向CPU发出中断请求INTt;CPU响应中断后,读出计数值M1,并将计数器清零重新计数。()”相关的问题

更多“M法的原理是由计数器记录PLG发出的脉冲信号;定时器每隔时间Tc向CPU发出中断请求INTt;CPU响应中断后,读出计数值M1,并将计数器清零重新计数。()”相关的问题

第1题

第6题

有一根U形导线,质量为m,两端浸没在水银槽中,导线的上段长l,处在磁感应强度为B的均匀磁场中,如图11-48所示。当接通电源时,这导线就会从水银槽中跳起来。假定电流脉冲的时间同导线上升时间相比非常小。(1)试由导线跳起所达到的高度h计算电流脉冲的电荷量q;(2)如B=0.1T,m=10g,l=20cm,h=0.3m,计算q的值。(提示:利用动量原理,找出∫Idt与∫Fdt的关系。)

第8题

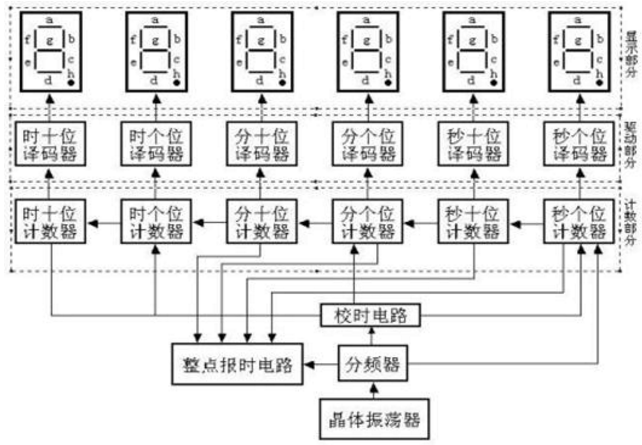

试设计一个数字电子钟,其原理框图如图9-10所示。秒信号用石英晶体振荡器(频率为32768Hz)加分频器来实现。译码显示电路将“时”、“分”、“秒”计数器的输出状态经七段显示译码器译码,通过6位LED七段显示器显示出来。整点报时电路是根据计时系统的输出状态产生一个脉冲信号,然后去触发音频发生器实现报时。校时电路是用来对“时”、“分”、“秒”显示数字进行校对调整的。

第9题

A.与定时器/计数器无关的寄存器是SCON

B.定时/计数器的定时功能是指对内部时钟计数

C.定时器T1溢出后,自动设置的标志位是TF1

D.关于TH0和TL0的叙述正确的是TH0存放计数值高8位,TL0存放计数值低8位

E.定时器工作在方式1时,其满值M为65536

F.可以启动定时/计数器开始工作的语句是TR0=1

第10题

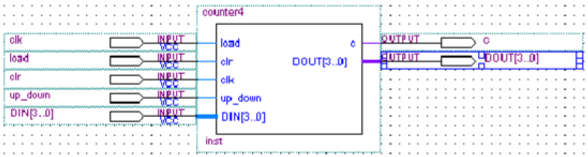

4位二进制加法计数器设计

实验要求

用原理图输入设计法或Verilog HDL文本输入设计法设计4位二进制加法计数器电路,建立4位二进制加法计数器的实验模式。通过电路仿真和硬件验证,进一步了解4位二进制加法计数器的功能和特性。

设计原理

4位二进制加法计数器的元件符号如图所示,CLK是时钟输入端,上升沿有效;CLRN是复位输入端,低电平有效;Q[3..0]是计数器的状态输出端;COUT是进位输出端。

第11题

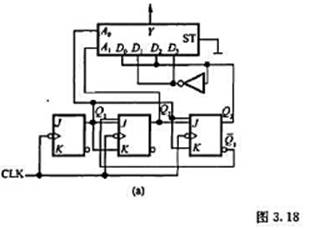

图3.18(a)是一种序列信号发生器电路,它由一个计数器和一个四选一数据选择器构成.分析计数器的工作原理,确定其模值和状态转换关系,确定在计数器输出控制下,数据选择器的输出序列.