题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

二输入端与非门器件74LS00与7400的逻辑功能完全相同.()

答案

答案

请输入或粘贴题目内容

搜题

请输入或粘贴题目内容

搜题

拍照、语音搜题,请扫码下载APP

拍照、语音搜题,请扫码下载APP

题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

答案

答案

更多“二输入端与非门器件74LS00与7400的逻辑功能完全相同.()”相关的问题

更多“二输入端与非门器件74LS00与7400的逻辑功能完全相同.()”相关的问题

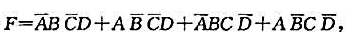

第1题

逻辑函数的与或表达式为 现要求用二输入与门和异或门两种器件来实现.请写出适合此要求的逻辑表达式,画出逻辑电路图.

现要求用二输入与门和异或门两种器件来实现.请写出适合此要求的逻辑表达式,画出逻辑电路图.

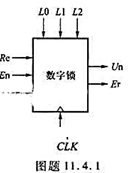

第3题

(1)画出系统的ASM图。

(2)画出系统的状态转换图。

(3)用Verilog HDL语言描述其工作过程。

提示:数字锁系统的示意图如图题11.4.1所示,由于开锁过程比较简单,所以没有划分控制单元和处理单元。L0、L1、L2用于从到高位设置密码,另外三个输入端Re,En,Ki中,Re是复位端,当Re=

1时,系统复位进入初始状态;En是控制井关,Ki是数据输入端,当按一下En键使En=1时,从Ki端输入一个数码,再按一下En键,再送一个数码,直到将三个数码送完为止。每输入一个数据都要同原设定的密码比较,依次从低位到高位进行。若相等则准备接收下一位数码,若不相等,系统应进入错误状态。输入数码的位数也是开锁的条件。当输入数码的位数和位值与相应密码都相等时,系统发出开锁信号Un=1,锁被打开,否则Er=1表示开锁过程错误。为保密起见,中间错误状态不显示,并且不能返回初态,直到三个数码全部送完为止。

第4题

A.增大发送端WBA的输入衰减

B.增大接收端WPA的输入衰减

C.在D32输入前加衰减

D.也在RWC输入前加固定衰减器解决

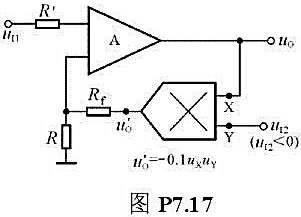

第5题

为了使图P7.17所示电路实现除法运算,(1)标出集成运放的同相输入端和反相输入端;(2)求出uo和uI1、uI2的运算关系式.

第10题

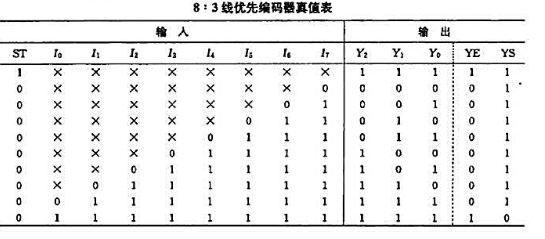

8:3线优先编码器真值表如下表所示,其中l0~I7为数据输入端(优先级I7为最高),ST为使能输入端,Y0~Y2为数据输出端,YE、YS为输出扩展端.用VHDL语言设计之.